August 1996, Rev D

FN7160

## Video Gain Control/Fader

# élantec.

The EL4094 is a complete two-input fader. It combines two inputs according to the equation:

$V_{OUT} = V_{INA} (0.5V + V_G) + V_{INB} (0.5V - V_G),$

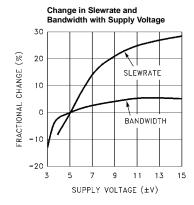

where  $V_{GAIN}$  is the difference between  $V_{GAIN}$  and  $\overline{V}_{\overline{GAIN}}$  pin voltages and ranges from -0.5V to +0.5V. It has a wide 60MHz bandwidth at -3dB, and is designed for excellent video distortion performance. The EL4094 is the same circuit as the EL4095, but with feedback resistors included on-chip to implement unity-gain connection. An output buffer is included in both circuits.

The gain-control input is also very fast, with a 20MHz small-signal bandwidth and 70ns recovery time from overdrive.

The EL4094 is compatible with power supplies from  $\pm 5V$  to  $\pm 15V$ , and is available in both the 8-pin plastic DIP and SO-8.

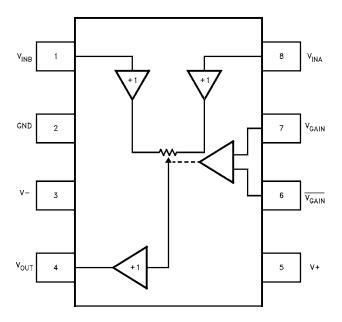

#### **Pinout**

### EL4094 (8-PIN PDIP, SO) TOP VIEW

Manufactured under U.S. Patent No. 5,321,371, 5,374,898

### **Features**

- · Complete video fader

- 0.02%/0.04° differential gain/phase @100% gain

- Output amplifier included

- · Calibrated linear gain control

- ±5V to ±15V operation

- · 60MHz bandwidth

- · Low thermal errors

## **Applications**

- Video faders/wipers

- · Gain control

- · Video text insertion

- · Level adjust

- Modulation

## **Ordering Information**

| PART<br>NUMBER | TEMP. RANGE    | PACKAGE    | PKG. NO. |

|----------------|----------------|------------|----------|

| EL4094CN       | -40°C to +85°C | 8-Pin PDIP | MDP0031  |

| EL4094CS       | -40°C to +85°C | 8-Pin SO   | MDP0027  |

## **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| $V_S$ +     | Voltage between V <sub>S</sub> + and GND                 | I <sub>OUT</sub> | Output Current                             |

|-------------|----------------------------------------------------------|------------------|--------------------------------------------|

| ٧s          | Voltage between V <sub>S</sub> + and V <sub>S</sub> +33V |                  | Internal Power Dissipation See Curves      |

| $V_{INA}$ , | Input Voltage (V <sub>S</sub> -) -0.3V                   | $T_A$            | Operating Ambient Temp. Range40°C to +85°C |

| $V_{INB}$   | to (V <sub>S</sub> +) +0.3V                              | $T_J$            | Operating Junction Temperature             |

| $V_{GAIN}$  | Input Voltage                                            | T <sub>ST</sub>  | Storage Temperature Range65°C to +150°C    |

| VCAIN       | Input Voltage Ve- to Ve+                                 |                  |                                            |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

### **Open-Loop DC Electrical Specifications**

$V_S=\pm5V,\,T_A=25^{\circ}C,\,V_{GAIN}=+0.6V$  to measure channel A,  $V_{GAIN}=-0.6V$  to measure channel B,  $\overline{V_{GAIN}}=0V$ , unless otherwise specified. NL,  $A_V=0.25V$

| PARAMETER                | DESCRIPTION                                                                  |           | UNITS |           |       |

|--------------------------|------------------------------------------------------------------------------|-----------|-------|-----------|-------|

|                          |                                                                              | MIN       | TYP   | MAX       | UNITS |

| Vos                      | Input Offset Voltage                                                         |           | 4     | 30        | mV    |

| I <sub>B</sub> +         | V <sub>IN</sub> Input Bias Current                                           |           | 2     | 10        | μA    |

| PSRR                     | Power Supply Rejection Ratio                                                 | 60        | 80    |           | dB    |

| EG                       | Gain Error, 100% Setting                                                     |           | -0.5  | -0.8      | %     |

| V <sub>IN</sub>          | V <sub>IN</sub> Range                                                        | (V-) +2.5 |       | (V+) -2.5 | V     |

| Vo                       | Output Voltage Swing                                                         | (V-) +2.5 |       | (V+) -2.5 | V     |

| I <sub>SC</sub>          | Output Short-Circuit Current                                                 | 50        | 95    | 150       | mA    |

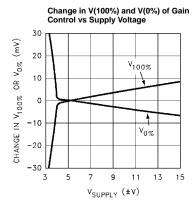

| V <sub>GAIN</sub> , 100% | Minimum Voltage at V <sub>GAIN</sub> for 100% Gain                           | 0.45      | 0.5   | 0.55      | V     |

| V <sub>GAIN</sub> , 0%   | Maximum Voltage at V <sub>GAIN</sub> for 0% Gain                             | -0.55     | -0.5  | -0.45     | V     |

| NL, Gain                 | Gain Control Non-linearity, V <sub>IN</sub> = ±0.5V                          |           | 1.5   | 4         | %     |

| NL, A <sub>V</sub> = 1   | Signal Non-linearity, V <sub>IN</sub> = 0 to ±1V, V <sub>GAIN</sub> = 0.55V  |           | 0.01  |           | %     |

| A <sub>V</sub> = 0.5     | Signal Non-linearity, V <sub>IN</sub> = 0 to ±1V, V <sub>GAIN</sub> = 0V     |           | 0.05  |           | %     |

| A <sub>V</sub> = 0.25    | Signal Non-linearity, V <sub>IN</sub> = 0 to ±1V, V <sub>GAIN</sub> = -0.25V |           | 0.2   | 0.5       | %     |

| R <sub>GAIN</sub>        | Resistance between $V_{\mbox{GAIN}}$ and $\overline{V}_{\mbox{GAIN}}$        | 4.6       | 5.5   | 6.6       | kΩ    |

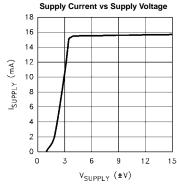

| I <sub>S</sub>           | Supply Current                                                               | 12        | 14.5  | 19        | mA    |

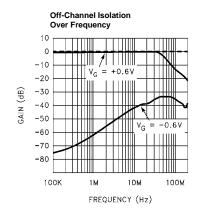

| F <sub>T</sub>           | Off-Channel Feedthrough                                                      |           | -75   | -50       | dB    |

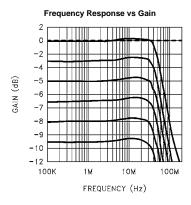

## Closed-Loop AC Electrical Specifications $V_S = \pm 15V$ , $C_L = 15pF$ , $T_A = 25^{\circ}C$ , $A_V = 100\%$ unless otherwise noted.

|           |                                                                     | LIMITS |     |     |       |

|-----------|---------------------------------------------------------------------|--------|-----|-----|-------|

| PARAMETER | DESCRIPTION                                                         | MIN    | TYP | MAX | UNITS |

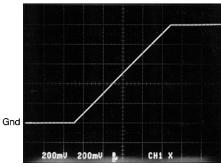

| SR        | Slew Rate; V <sub>OUT</sub> from -3V to +3V measured at -2V and +2V | 370    | 500 |     | V/µs  |

| BW        | Bandwidth,<br>-3dB                                                  | 45     | 60  |     | MHz   |

|           | -1dB                                                                |        | 35  |     | MHz   |

|           | -0.1dB                                                              |        | 6   |     | MHz   |

## **Closed-Loop AC Electrical Specifications**

$V_S = \pm 15 V$ ,  $C_L = 15 pF$ ,  $T_A = 25 ^{\circ}C$ ,  $A_V = 100 \%$  unless otherwise noted. (Continued)

|                         |                                                                               | LIMITS |      |     |       |

|-------------------------|-------------------------------------------------------------------------------|--------|------|-----|-------|

| PARAMETER               | DESCRIPTION                                                                   | MIN    | TYP  | MAX | UNITS |

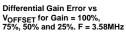

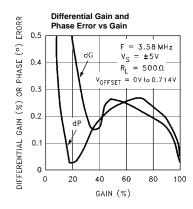

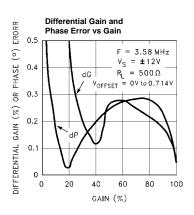

| dG                      | Differential Gain, AC amplitude of 286mV <sub>P-P</sub>                       |        |      |     |       |

|                         | at 3.58MHz on DC offset of -0.7, 0, and +0.7V A <sub>V</sub> = 100%           |        | 0.02 |     | %     |

|                         | A <sub>V</sub> = 50%                                                          |        | 0.20 |     | %     |

|                         | A <sub>V</sub> = 25%                                                          |        | 0.40 |     | %     |

| dθ                      | Differential Phase, AC amplitude of 286mV <sub>P-P</sub>                      |        |      |     |       |

|                         | at 3.58MHz on DC offset of -0.7, 0, and +0.7V A <sub>V</sub> = 100%           |        | 0.04 |     | (°)   |

|                         | A <sub>V</sub> = 50%                                                          |        | 0.20 |     | (°)   |

|                         | A <sub>V</sub> = 25%                                                          |        | 0.20 |     | (°)   |

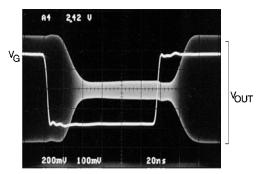

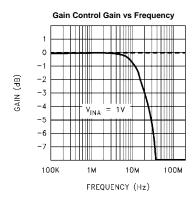

| BW, GAIN                | -3dB Gain Control Bandwidth, V <sub>GAIN</sub> Amplitude 0.5 V <sub>P-P</sub> |        | 20   |     | MHz   |

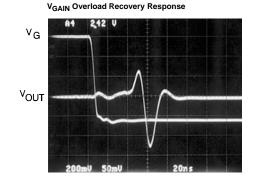

| T <sub>REC</sub> , GAIN | Gain Control Recovery from Overload; V <sub>GAIN</sub> from -0.6V to 0V       |        | 70   |     | ns    |

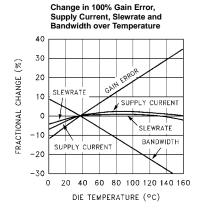

## **Typical Performance Curves**

Large-Signal Step Response for Gain = 100%, 50%, 25%, and 0%.  $V_S \pm 12V$

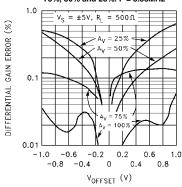

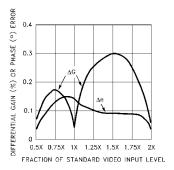

Differential Gain Error vs V<sub>OFFSET</sub> for Gain = 100%, 75%, 50% and 25%. F = 3.58MHz

# Nonlinearity vs V<sub>IN</sub> for Gain = 100%, 75%, 50% and 25%

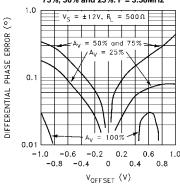

#### Differential Phase Error vs V<sub>OFFSET</sub> for Gain = 100%, 75%, 50% and 25%. F = 3.58MHz

#### Differential Phase Error vs V<sub>OFFSET</sub> for Gain = 100%, 75%, 50% and 25%. F = 3.58MHz

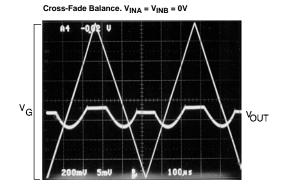

Gain Control Response to a Non-Overloading Step, Constant Sinewave at  $\mathbf{V}_{\text{INA}}$

## Applications Information

The EL4094 is a self-contained and calibrated fader subsystem. When a given channel has 100% gain the circuit behaves as a current-feedback amplifier in unity-gain connection. As such, video and transfer distortions are very low. As the gain of the input is reduced, a 2-quadrant multiplier is gradually introduced into the signal path and distortions increase with reducing gain.

The input impedance also changes with gain setting, from about  $1M\Omega$  at 100% gain down to  $16k\Omega$  at zero gain. To

maximize gain accuracy and linearity, the inputs should be driven from source impedances of  $500\Omega$  or less.

### Linearity

The EL4094 is designed to work linearly with ±2V inputs, but lowest distortion occurs at ±1V levels and below. Errors are closer to those of a good current-feedback amplifier above 90% gain.

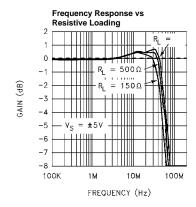

Low-frequency linearity is 0.1% or better for gains 25% to 100% and inputs up to 1V. NTSC differential gain and phase errors are better than 0.3% and 0.3° for the 25% to 100% gain range. These distortions are not strongly affected by

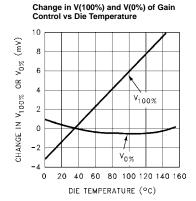

supply voltage nor output loading, at least down to  $150\Omega$ . For settling to 0.1%, however, it is best to not load the output heavily and to run the EL4094 on the lowest practical supply voltages, so that thermal effects are minimized.

### Gain Control Inputs

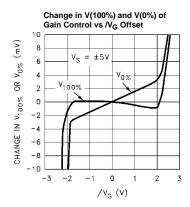

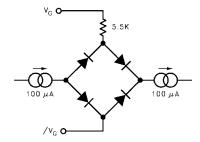

The gain control inputs are differential and may be biased at any voltage as long as  $\overline{V}_{\overline{GAIN}}$  is less than 2.5V below V+ and 3V above V-. The differential input impedance is  $5.5k\Omega$ , and the common-mode impedance is more than  $500k\Omega$ . With zero differential voltage on the gain inputs, both signal inputs have a 50% gain factor. Nominal calibration sets the 100% gain of V<sub>INA</sub> input at +0.5V of gain control voltage, and 0% at -0.5V of gain control.  $\ensuremath{\text{V}_{\text{INB}}}$  's gain is complementary to that of  $V_{INA}$ ; +0.5V of gain control sets 0% gain at  $V_{INB}$  and -0.5V gain control sets 100% V<sub>INB</sub> gain. The gain control does not have a completely abrupt transition at the 0% and 100% points. There is about 10mV of "soft" transfer at the gain endpoints. To obtain the most accurate 100% gain factor or best attenuation at 0% gain, it is necessary to overdrive the gain control input by 30mV or more. This would set the gain control voltage range as -0.565V to +0.565V, or 30mV beyond the maximum guaranteed 0% to 100% range. In fact, the gain control inputs are very complex. Here is a representation of the terminals:

FIGURE 1. REPRESENTATION OF GAIN CONTROL INPUTS  $V_G$  AND  $/V_G$

For gain control inputs between ±0.5V (±90µA), the diode bridge is a low impedance and all of the current into  $V_G$  flows back out through/ $V_G$ . When gain control inputs exceed this amount, the bridge becomes a high impedance as some of the diodes shut off, and the  $V_G$  impedance rises sharply from the nominal  $5.5 \mbox{K}\Omega$  to about  $500 \mbox{K}\Omega$ . This is the condition of gain control overdrive. The actual circuit produces a much sharper overdrive characteristic than does the simple diode bridge of this representation.

The gain input has a 20MHz -3dB bandwidth and 17ns risetime for inputs to  $\pm 0.45$ V. When the gain control voltage exceeds the 0% or 100% values, a 70ns overdrive recovery transient will occur when it is brought back to linear range. If quicker gain overdrive response is required, the Force control inputs of the EL4095 can be used.

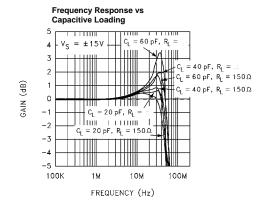

### **Output Loading**

The EL4094 does not work well with heavy capacitive loads. Like all amplifier outputs, the output impedance becomes inductive over frequency resonating with a capacitive load. The effective output inductance of the EL4094 is about 350nH. More than 50pF will cause excessive frequency response peaking and transient ringing. The problem can be solved by inserting a low-value resistor in series with the load,  $22\Omega$  or more. If a series resistance cannot be used, then adding a  $300\Omega$  or less load resistor to ground or a "snubber" network may help. A snubber is a resistor in series with a capacitor,  $150\Omega$  and 100pF being typical values. The advantage of a snubber is that it does not draw DC load current.

Unterminated coaxial line loads can also cause resonances, and they should be terminated either at the far end or a series back-match resistor installed between the EL4094 and the cable.

The output stage can deliver up to 140mA into a short-circuit load, but it is only rated for a continuous 35mA. More continuous current can cause reliability problems with the on-chip metal interconnect. Video levels and loads cause no problems at all.

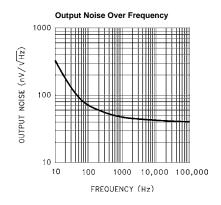

#### Noise

The EL4094 has a very simple noise characteristic: the output noise is constant ( $40\text{nV}/\sqrt{\text{Hz}}$  wideband) for all gain settings. The input-referred noise is then the output noise divided by the gain. For instance, at a gain of 50% the input noise is  $40\text{nV}/\sqrt{\text{Hz}/0.5}$ , or  $80\text{nV}/\sqrt{\text{Hz}}$ .

### Bypassing

The EL4094 is fairly tolerant of power-supply bypassing, but best multiplier performance is obtained with closely connected 0.1µF ceramic capacitors. The leaded chip capacitors are good, but neither additional tantalums nor chip components are necessary. The signal inputs can oscillate locally when connected to long lines or unterminated cables.

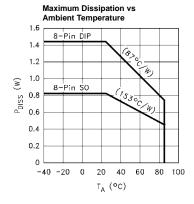

### **Power Dissipation**

Peak die temperature must not exceed 150°C. At this temperature, the epoxy begins to soften and becomes unstable, chemically and mechanically. This allows 75°C internal temperature rise for a 75°C ambient. The EL4094 in the 8-pin PDIP package has a thermal resistance of 87°/W, and can thus dissipate 862mW at a 75°C ambient temperature. The device draws 17mA maximum supply current, only 510mW at  $\pm$ 15V supplies, and the circuit has no dissipation problems in this package.

The SO-8 surface-mount package has a 153°/W thermal resistance with the EL4094, and only 490mW can be dissipated at 75°C ambient temperature. The EL4094 thus cannot be operated with ±15V supplies at 75°C in the surface-mount package; the supplies should be reduced to

±5V to ±12V levels, especially if extra dissipation occurs when driving a load.

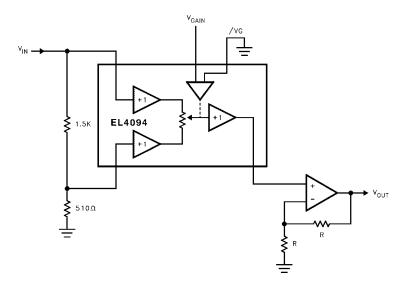

### The EL4094 as a Level Adjust

A common use for gain controls is as an input signal leveller—a circuit that scales too-large or too-small signals to a standard amplitude. A typical situation would be to scale a variable video input by +6dB to -6dB to obtain a standard amplitude. The EL4094 cannot provide more than 0dB gain, but it can span the range of 0dB to -12dB with another amplifier gaining the output up by 6dB. The simplest way to obtain the range is to simply ground the B input and vary the gain of the signal applied to the A input. The disadvantage of this approach is that linearity degrades at low gains. By connecting the signal to the A input of the EL4094 and the signal attenuated by 12dB to the B input, the gain control offers the highest linearity possible at 0dB and -12dB extremes, and good performance between. The circuit is shown on the following page.

The EL4095 can be used to provide the required gains without the extra amplifier. In practice, the gain control is adjusted to set a standard video level regardless of the input level. The EL4583 sync-separator has a recovered amplitude output that can be used to servo the gain control voltage. Here is the curve of differential gain and phase

distortion for varying inputs, with the output set to standard video level:

FIGURE 2. DIFFERENTIAL GAIN AND PHASE OF LINEARIZED LEVEL CONTROL

The differential gain error is kept to 0.3% and the differential phase to 0.15° or better over the entire input range.

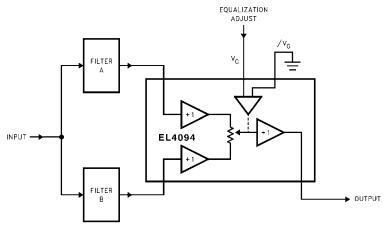

## The EL4094 as an Adjustable Filter

Equalizers are used to adjust the delay or frequency response of systems. A typical use is to compensate for the high-frequency loss of a cable system ahead of the cable so as to create a flat response at the far end. A generalized scheme with the EL4094 is shown below.

FIGURE 3. +6dB to -6dB LINEARIZED LEVEL CONTROL

FIGURE 4. GENERAL ADJUSTABLE EQUALIZER

For an adjustable preemphasis filter, for instance, filter A might be an all-pass filter to compensate for the delay of filter B, a peaking filter. Fading the gain from A to B provides a variable amount of peaking, but constant delay.

### The EL4094 as a Phase Modulator

To make a phase modulator, filter A might be a leading-phase network, and filter B a lagging network. The wide bandwidth of the gain-control input allows wideband phase modulation of the carrier applied to the main input. Of course, the carrier and gain inputs must not be digital but be reasonably clean sinewaves for the modulation to be accurate.

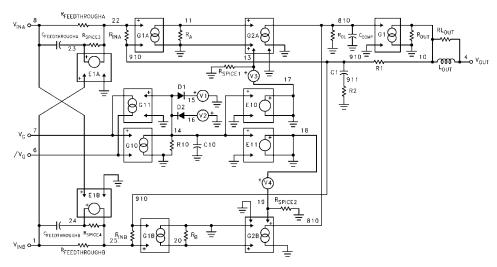

## EL4094 Macromodel

This macromodel is offered to allow simulation of general EL4094 behavior. We have included these characteristics:

- Small-signal frequency response

- Output loading effects

- Input impedance

- Off-channel feedthrough

- Output impedance over frequency

- Signal path DC distortions

- VGAIN I-V characteristics

- V<sub>GAIN</sub> overdrive recovery delay

- 100% gain error

These will give a good range of results for various operating conditions, but the macromodel does not behave identically as the circuit in these areas:

- Temperature effects

- Signal overload effects

- Signal and V̄<sub>G</sub> operating range

- Current-limit

- Video and high-frequency distortions

- Supply voltage effects

- Slewrate limitations

- Noise

- Power supply interactions

The macromodel's netlist is based on the Pspice simulator (copywritten by the Microsim Company). Other simulators may not support the POLY function, which is used to implement multiplication as well as square-low nonlinearities.

FIGURE 5. GEL4094 MACROMODEL SCHEMATIC

## EL4094 Macromodel

```

V<sub>INB</sub>

V<sub>OUT</sub>

Л

/V<sub>G</sub>

V<sub>G</sub>

\mathsf{V}_{\mathsf{INA}}

8)

.subckt EL4094subckt (1

6

R<sub>OL</sub> 810 0 290k

Ccomp 810 0 3.5p

G1 10 0 810 0 -10

R<sub>OUT</sub> 10 0 0.1

L<sub>OUT</sub> 10 4 350.200n

RL<sub>OUT</sub> 10 4 80

r1 10 910 10

c1 910 911 300p

r2 911 0 90

*** Input channel A

R<sub>INA</sub> 22 910 16k

ra 11 0 1k

Cfeedthrougha 23 8 130p

Rfeedthrougha 8 22 1.0

Ela 23 22 1 0 1.0

Rspice3 23 22 1E12

G1a110POLY(1)(22, 910)0.00.001-3E-6

G2a8100POLY(2)(11,0)(13, 0)0.00.00.00.00.001

***Input channel B

R<sub>INB</sub> 25 910 16k

rb 20 0 1k

Cfeedthroughb 24 1 130p

```

Rfeedthroughb 1 25 1.0 E1b 24 25 8 0 1.0 Rspice4 24 25 1E12 G1b200POLY(1)(25, 910)0.00.001-3E-6 G2b8100POLY(2)(20,0)(19, 0)0.00.00.00.00.001 \*\*\*Gain control Rspice1 13 0 1E12 Rspice2 18 0 1E12 R10 14 0 1E7 C10 14 0 8E-16 D1 14 15 Dclamp D2 16 14 Dclamp .model Dclamp D (TT=200n) V1 15 0 4999.3 V2 0 16 4999.3 V3 13 17 0.5 V4 19 18 0.5 G10 14 0 7 6 -0.001 G11 7 6 14 0 -2E-8 E10 17 0 14 0 1E-4 E11 18 0 14 0 -1E-4 .ends

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com